## Electronic and photonic IC co-design for high-speed optical transceivers

<u>Johan Bauwelinck</u><sup>a</sup>, M. Verbeke<sup>a</sup>, J. Lambrecht<sup>a</sup>, M. Vanhoecke<sup>b</sup>, L. Breyne<sup>c</sup>, G. Coudyzer<sup>a</sup>, J. Declercq<sup>a</sup>, B. Moeneclaey<sup>a</sup>, N. Singh<sup>a</sup>, C. Bruynsteen<sup>a</sup>, C. Wang<sup>a</sup>, S. Niu<sup>a</sup>, X. Wang<sup>a</sup>, T. Pannier<sup>a</sup>, Y. Gu<sup>a</sup>, A. Vandierendonck<sup>a</sup>, K. De Bruyn<sup>a</sup>, J. Van Kerrebrouck<sup>a</sup>, M. Verplaetse<sup>c</sup>, G. Torfs<sup>a</sup>, X. Yin<sup>a</sup>, P. Ossieur<sup>a</sup>

<sup>a</sup> IDLab, Dep. INTEC, Ghent University - imec, 9052 Ghent, Belgium

<sup>b</sup>Now with Nvidia, 9000 Ghent, Belgium

<sup>c</sup>Now with Nokia Bell Labs, 2018 Antwerp, Belgium

\* Corresponding author: johan.bauwelinck@ugent.be

New circuit architectures and technologies for high-speed electronic and photonic integrated circuits are essential to realize optical interconnects with higher symbol rate. As a consequence of the increasing speeds, close integration and co-design of photonic and electronic chips have become a necessity to realize high-performance transceivers with novel packaging approaches.

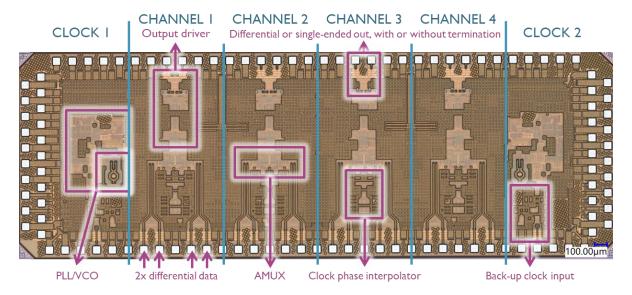

This presentation will illustrate a number of recent developments of application-specific high-speed electro-optic transceiver circuits including e.g. broadband driver amplifiers, multiplexer circuits and transimpedance amplifiers for signal generation and reception at 100 Gbaud and beyond. Fig. 1 shows such a recent example of a highly integrated SiGe BiCMOS chip including a quad channel 106 Gbaud 2-to-1 analog multiplexer with a reconfigurable modulator driver (supporting both differential and single-ended operation, and with removable internal back-terminations) and including a 53 GHz clock generator (phase-locked loop, PLL; voltage controlled oscillator, VCO). The basic concepts and architectures, technological aspects, design challenges and trade-offs will be discussed.

Fig. 1: Micrograph of a quad channel 106 Gbaud 2-to-1 analog multiplexer with reconfigurable modulator driver, VCO/PLL clock generator and clock tree

## Acknowledgement

This work was supported in part by the EU-funded H2020 Projects Poetics under Grant 871769, Plasmoniac under Grant 871391, Nebula under Grant 871658, Caladan under Grant 825453, and the Metrograph Spearhead project under Grant 881603. This work was also supported by the Special Research Fund (BOF) of Ghent University and the Research Foundation Flanders (FWO) under Grant G0D7519N.